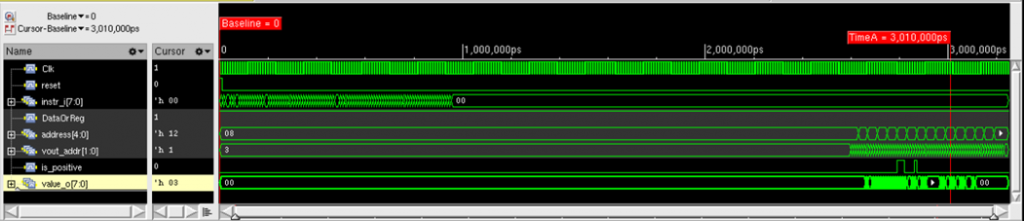

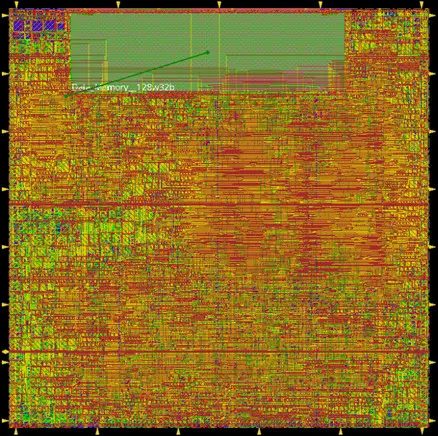

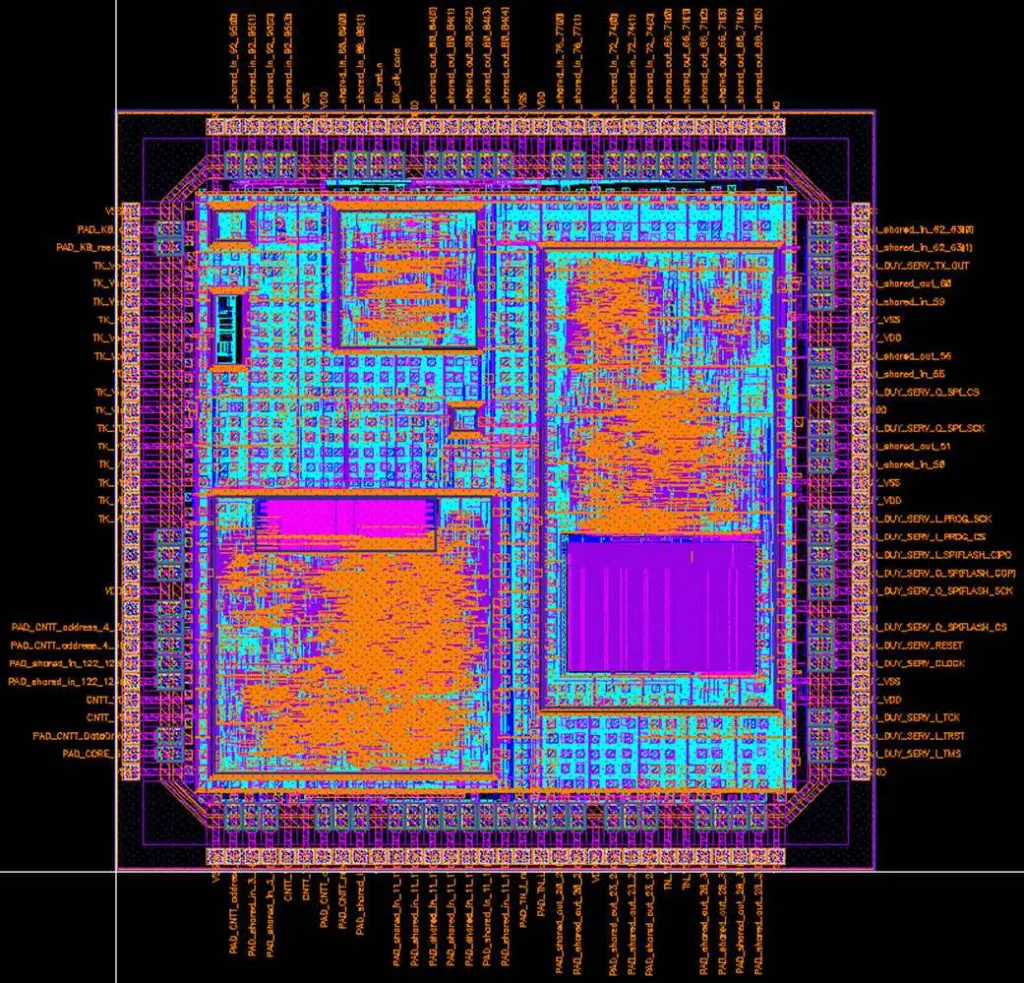

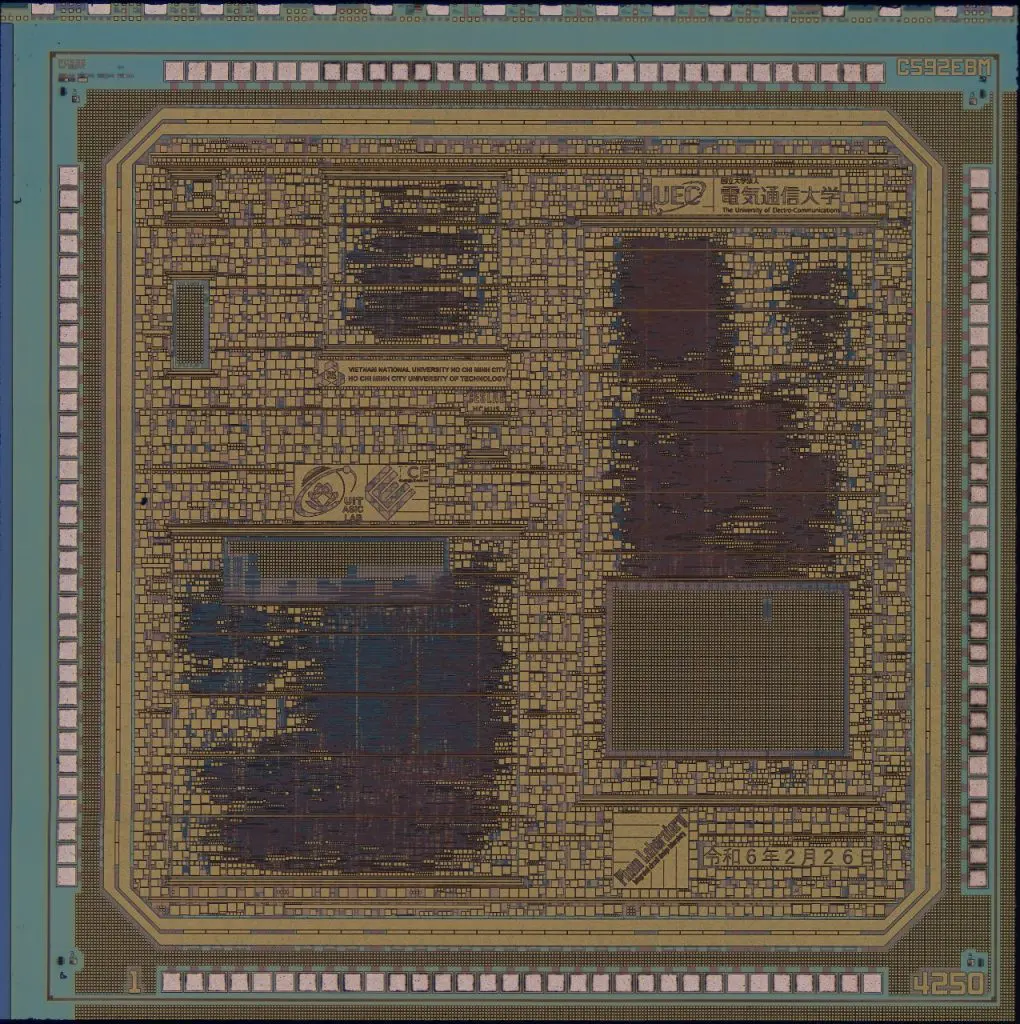

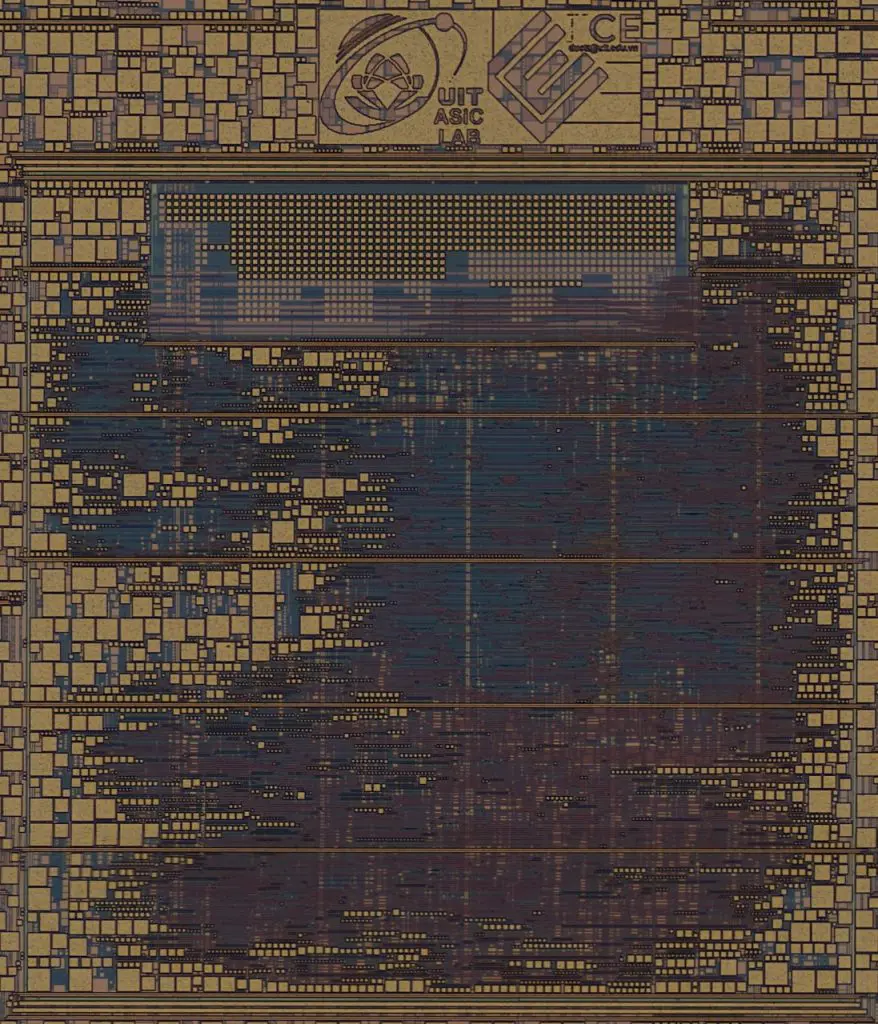

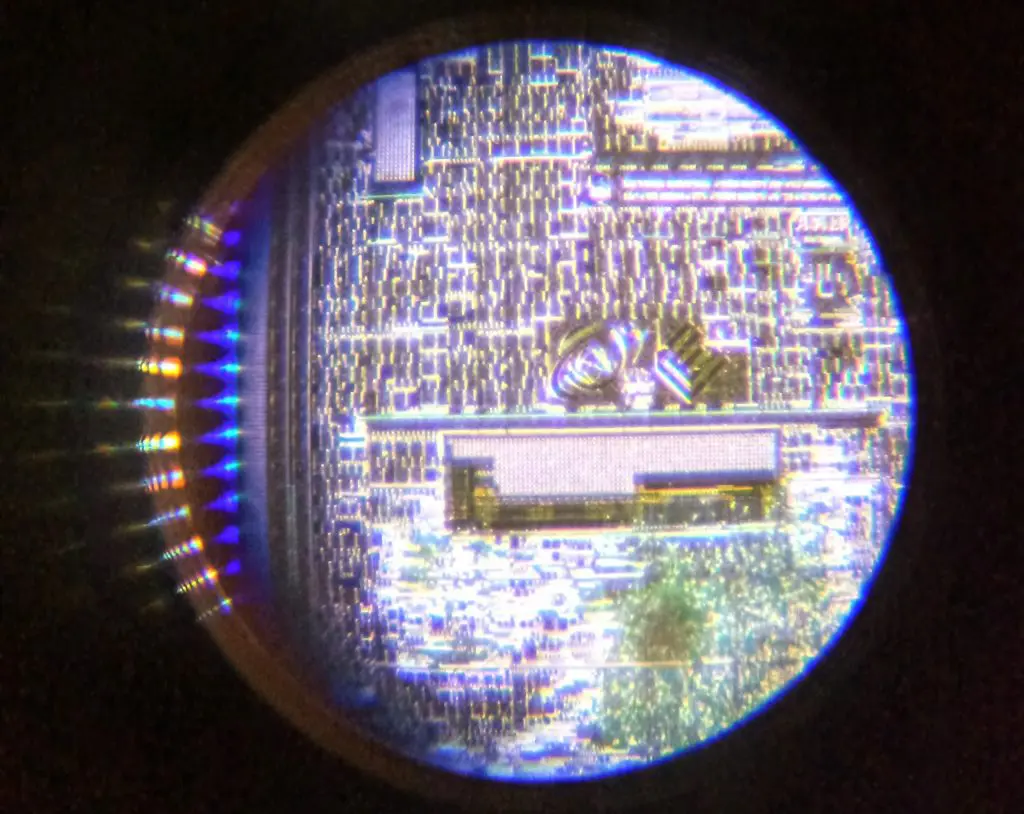

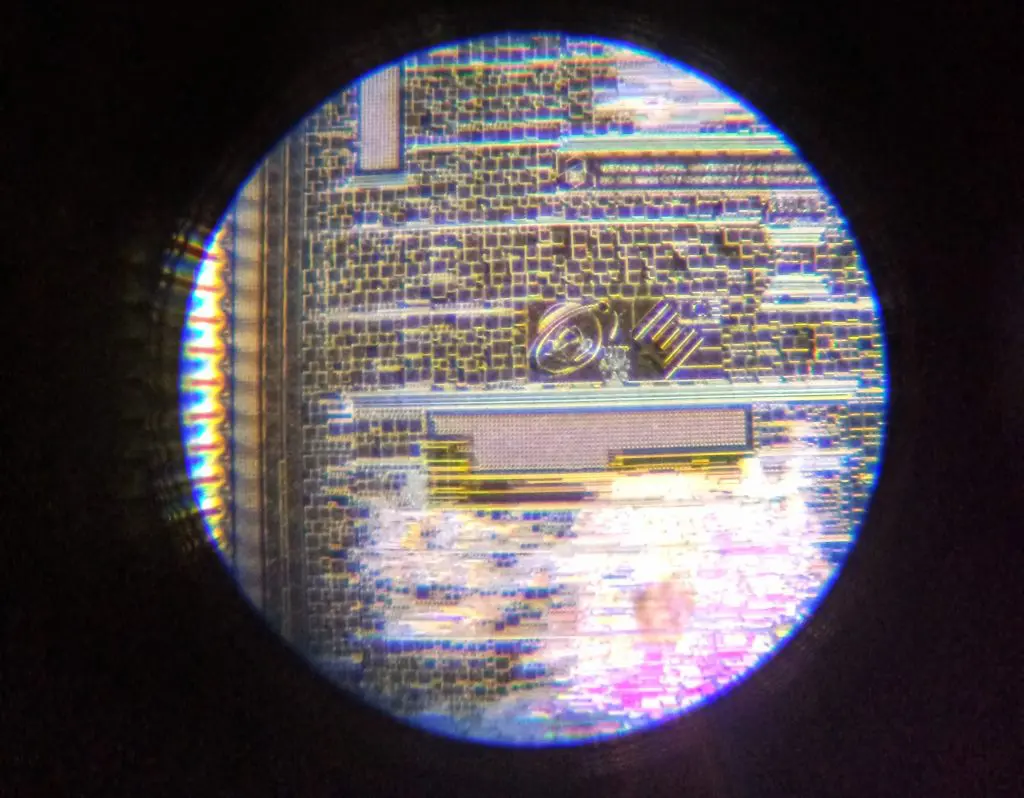

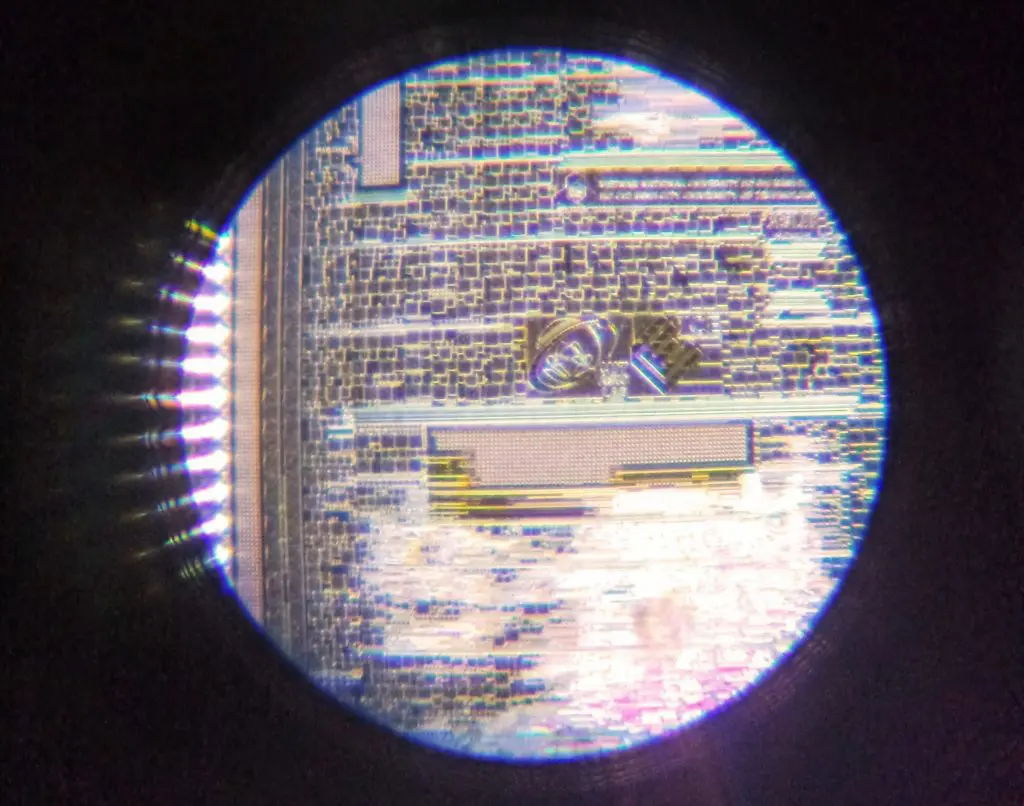

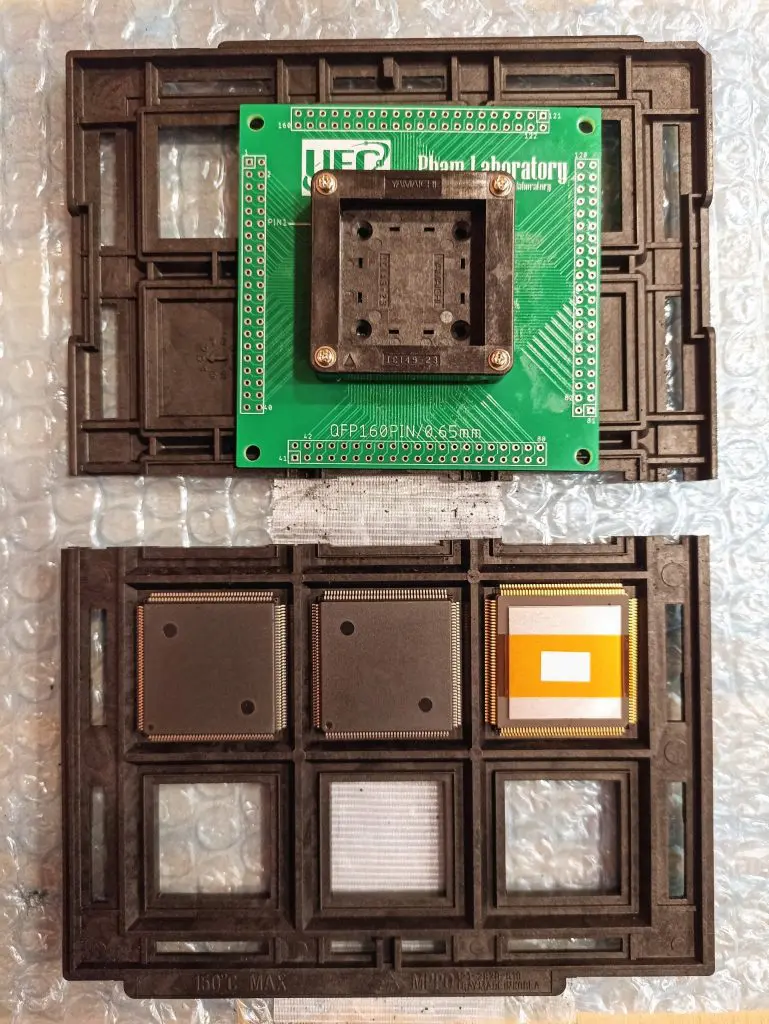

Sau giai đoạn thử nghiệm thành công, bộ vi xử lý tiếp tục được tổng hợp, thiết kế vật lý, sign-off và chế tạo với sự hỗ trợ quý báu từ Pham Laboratory. Mẫu chip hoàn thiện cuối cùng đã được Pham Laboratory, UEC, Nhật Bản, trao lại cho ASICLAB để tiến hành các bước đo kiểm và nghiên cứu tiếp theo.

Đề tài này là một phần trong nỗ lực nâng cao khả năng nghiên cứu và đào tạo trong lĩnh vực vi mạch bán dẫn, đóng góp vào sự phát triển của ngành Thiết kế vi mạch tại Khoa Kỹ thuật Máy tính. Đại học Quốc gia TP. Hồ Chí Minh đã quyết định cho phép mở tuyển sinh đào tạo thí điểm ngành này từ năm 2024, khẳng định vị thế của Trường Đại học Công nghệ Thông tin trong việc nghiên cứu, thiết kế và chế tạo vi mạch.

Đây là kết quả hợp tác nghiên cứu giữa Trường Đại học Điện tử Truyền thông (UEC), Tokyo, Nhật Bản và ASICLAB, Khoa Kỹ thuật Máy tính, Trường Đại học Công nghệ Thông tin, ĐHQG-HCM (UIT). Chip được UEC chế tạo bằng công nghệ CMOS.